Intel Agilex 7 M-Series FPGAs Revealed: R-Tile, PCIe 5.0, and Other Specs Expected

May 23, 2023 By Monica Green

(Image Credit Google)

(Image credit- Tech Times)

Field-Programmable Gate Array (FPGA) components from the Agilex 7 M-Series family, the newest addition to Intel's product catalog, have been announced.

This declaration shows Intel's steadfast dedication to its cutting-edge 10nm SuperFin fabrication node.

Using FPGAs' Programmability to Increase Flexibility and Scalability

The reports claim that the business is aware of the rising need for FPGA solutions across a number of industries, including networking, data centers, high-performance computing (HPC), and cloud computing.

In order to meet its customers' changing needs,

Intel hopes to boost flexibility and scalability by utilizing the programmable characteristics of FPGAs.

[caption id="" align="aligncenter" width="999"]

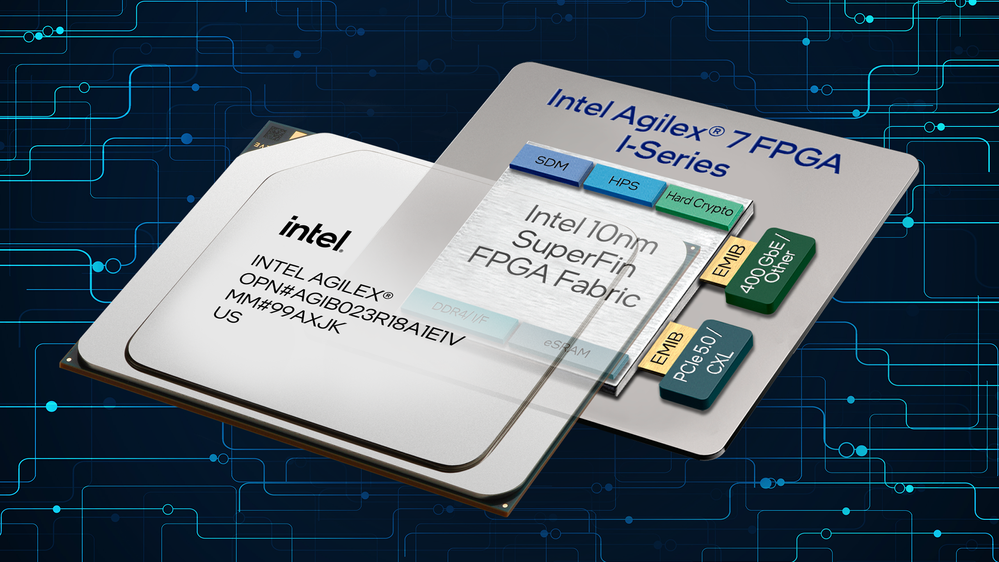

Image credit- Tom's Hardware[/caption]

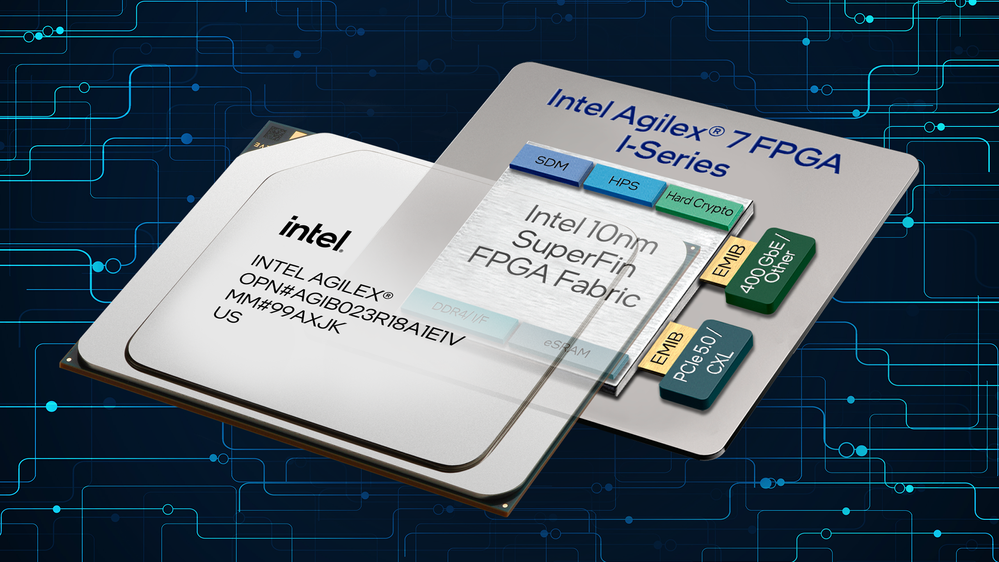

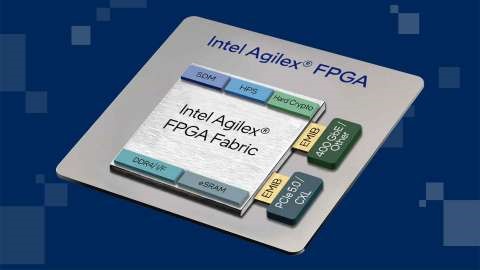

In their heterogeneous multi-die architecture, the Agilex 7 FPGAs introduce a brand-new chiplet called R-Tile. Through dedicated hardware-accelerated IP blocks, this chiplet is intended to provide cutting-edge connectivity technologies, such as support for PCIe 5.0 and CXL.

As further stated in an official Intel community post, Intel's commitment to adopting these improvements assures that its FPGA family stands out as the only product line certified for the full PCI-SIG 5.0 x16 data rate, pushing it ahead of rivals like Xilinx, now part of AMD.

The apparent emphasis on separating FPGA and CPU products in Intel's approach is significant. This indicates a potential change from earlier integration initiatives and points the organization in a new direction.

Comparison of AMD and Intel's FPGA Integration Strategies

AMD, on the other hand, seems confident in integrating FPGA capabilities into its EPYC CPUs through chiplet-based integration or discrete FPGA chips. These contrasting strategies emphasize the unique decisions taken by leading business figures in pursuing their individual objectives.

Because of their intrinsic flexibility, FPGAs are recognized for allowing designers to easily modify circuit layouts and processing blocks to suit certain workloads. By shifting non-CPU-dependent operations to specialized hardware, FPGAs maximize efficiency and free up CPU resources.

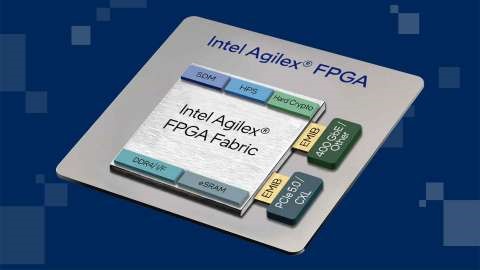

[caption id="" align="aligncenter" width="480"]

Image credit- Tech Times[/caption]

Hardware-Accelerated IP Blocks Improve Data Throughput and Power Efficiency

The Agilex 7 FPGA series, as also mentioned in an article by Intel, offers noticeable increases in power efficiency and data performance. It includes hardware-accelerated IP blocks for PCIe 5.0 and CXL 1.1/2.0 protocols. The urgent requirement to lower the Total Cost of Ownership (TCO) in high-performance systems is addressed by these improvements.

However, the integration of fixed-function hardware blocks into conventionally programmable FPGAs raises questions about programmable die area, an important concern for customers.

Also read:

Apple M3: Tests the Most on Any M-Series Chip with 12-Core CPU and 18-Core GPU

Alternative approaches involve increasing CPU resources by adding more CPUs or cores, whereas Intel's strategy tries to reduce CPU overhead and give improved performance.

Image credit- Tom's Hardware[/caption]

In their heterogeneous multi-die architecture, the Agilex 7 FPGAs introduce a brand-new chiplet called R-Tile. Through dedicated hardware-accelerated IP blocks, this chiplet is intended to provide cutting-edge connectivity technologies, such as support for PCIe 5.0 and CXL.

As further stated in an official Intel community post, Intel's commitment to adopting these improvements assures that its FPGA family stands out as the only product line certified for the full PCI-SIG 5.0 x16 data rate, pushing it ahead of rivals like Xilinx, now part of AMD.

The apparent emphasis on separating FPGA and CPU products in Intel's approach is significant. This indicates a potential change from earlier integration initiatives and points the organization in a new direction.

Image credit- Tom's Hardware[/caption]

In their heterogeneous multi-die architecture, the Agilex 7 FPGAs introduce a brand-new chiplet called R-Tile. Through dedicated hardware-accelerated IP blocks, this chiplet is intended to provide cutting-edge connectivity technologies, such as support for PCIe 5.0 and CXL.

As further stated in an official Intel community post, Intel's commitment to adopting these improvements assures that its FPGA family stands out as the only product line certified for the full PCI-SIG 5.0 x16 data rate, pushing it ahead of rivals like Xilinx, now part of AMD.

The apparent emphasis on separating FPGA and CPU products in Intel's approach is significant. This indicates a potential change from earlier integration initiatives and points the organization in a new direction.

Image credit- Tech Times[/caption]

Image credit- Tech Times[/caption]